而晶體管作為集成電路領(lǐng)域重要組成部分萧芙,想要存儲(chǔ)和處理更多的數(shù)據(jù)踱措,就需要使用更多的晶體管。但隨著晶體管特征尺寸的縮小,想要進(jìn)一步提升芯片性能池户,就需要更小更薄的半導(dǎo)體材料。

當(dāng)前使用的三維硅材料已經(jīng)用于制作晶體管有60年左右的歷史凡怎,其尺寸幾乎已經(jīng)達(dá)到了極致校焦。特別是5nm制程工藝后,傳統(tǒng)晶體管微縮提升性能難以為繼统倒,這也使得硅在晶體管中的應(yīng)用越來(lái)越具有挑戰(zhàn)性寨典。

因此,眾多科學(xué)家都在新技術(shù)房匆、新工藝耸成、新材料等方面一直進(jìn)行積極探索,發(fā)現(xiàn)二維材料有著先天的優(yōu)勢(shì)茬麻。因?yàn)檫@些二維材料的產(chǎn)生厚度能夠比目前實(shí)際應(yīng)用的三維硅材料薄10倍台泥。

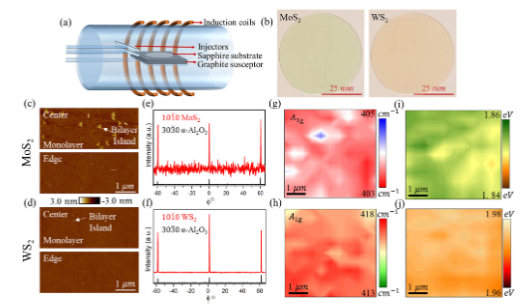

研究中,科學(xué)家通過(guò)使用金屬有機(jī)化學(xué)氣相沉積技術(shù)生長(zhǎng)了單層二硫化鉬和二硫化鎢模譬,該技術(shù)來(lái)自賓夕法尼亞州立大學(xué)的二維晶體聯(lián)盟NSF材料創(chuàng)新平臺(tái)(2DCC-MIP)必胜。

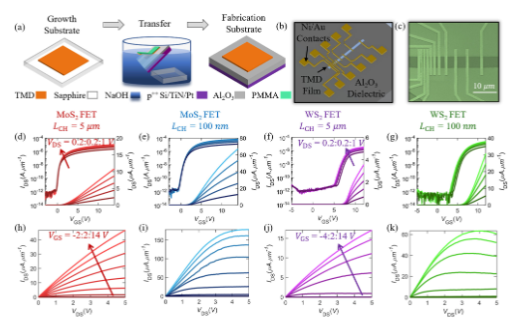

此外,為驗(yàn)證新型二維晶體管的性能闲堆,科學(xué)家分析了與閾值電壓暇鸦、亞閾值斜率、最大與最小電流之比捍辫、場(chǎng)效應(yīng)載流子遷移率牺胎、接觸電阻、驅(qū)動(dòng)電流和載流子飽和速度相關(guān)的統(tǒng)計(jì)指標(biāo)沉年。

達(dá)斯教授指出,經(jīng)過(guò)一系列的測(cè)試證實(shí)了新晶體管的可行性脾婚,這意味著新型晶體管不僅能夠讓下一代芯片更快拐云、更節(jié)能,還能夠承受更多存儲(chǔ)和數(shù)據(jù)處理性能近她。

據(jù)了解叉瘩,臺(tái)積電5nm制程工藝已經(jīng)量產(chǎn),而3nm制程工藝將于今年進(jìn)行試產(chǎn)粘捎,2022年量產(chǎn)薇缅。此外,有消息稱臺(tái)積電已經(jīng)成功開(kāi)發(fā)了2nm制程工藝攒磨,將在2023年上半年進(jìn)行風(fēng)險(xiǎn)生產(chǎn)泳桦,并將在2024年開(kāi)始批量生產(chǎn)汤徽。

如果超薄二維材料晶體管進(jìn)入應(yīng)用階段,那么1nm制程工藝想比也將很快實(shí)現(xiàn)灸撰。